在FPGA中���,动态相位调解(DPA)主要实现LVDS接口接收时对时钟和数据通道的相位赔偿���,以抵达正确接收的目的��。在LVDS输入接收时���,随着单线传输速率不绝接近于1 Gb/s���,使每位所占的时间窗不绝减小���,导致采样时钟对信号线的采样点很难在其有效区间进行准确采样����;再加上传输路径的差别���,各数据线和采样时钟抵达接收端的延迟时间不可包管完全一致���,从而带来了各信号线之间的位偏移(Bit Skew)和字偏移(Word Skew)���,如下图所示��。

位偏移为采样时钟沿不在各数据窗口的中心位置采样���,可能会导致数据采样坚持时间不敷长���,易使bit位爆发瞬间突变���,从而导致接收的数据不稳定����;字偏移是指采样接收后的各数据信号之间差别步���,使得同时在发送端发送的数据在接收端却不可同一时刻被采样���,导致接收的数据无效��。因此我们可能需要将时钟的相位做出调解���,使得时钟能稳定的收罗到输入的数据��。事情的焦点就是锁相环PLL的相位调解功效���,爆发时钟的差别相位���,接着看哪些相位能正确地收罗到输入数据���,然后取窗口中间的一个时钟相位���,作为正常事情时的采样时钟��。这样接口上具有最大的时序裕量���,从而包管链路的可靠性��。

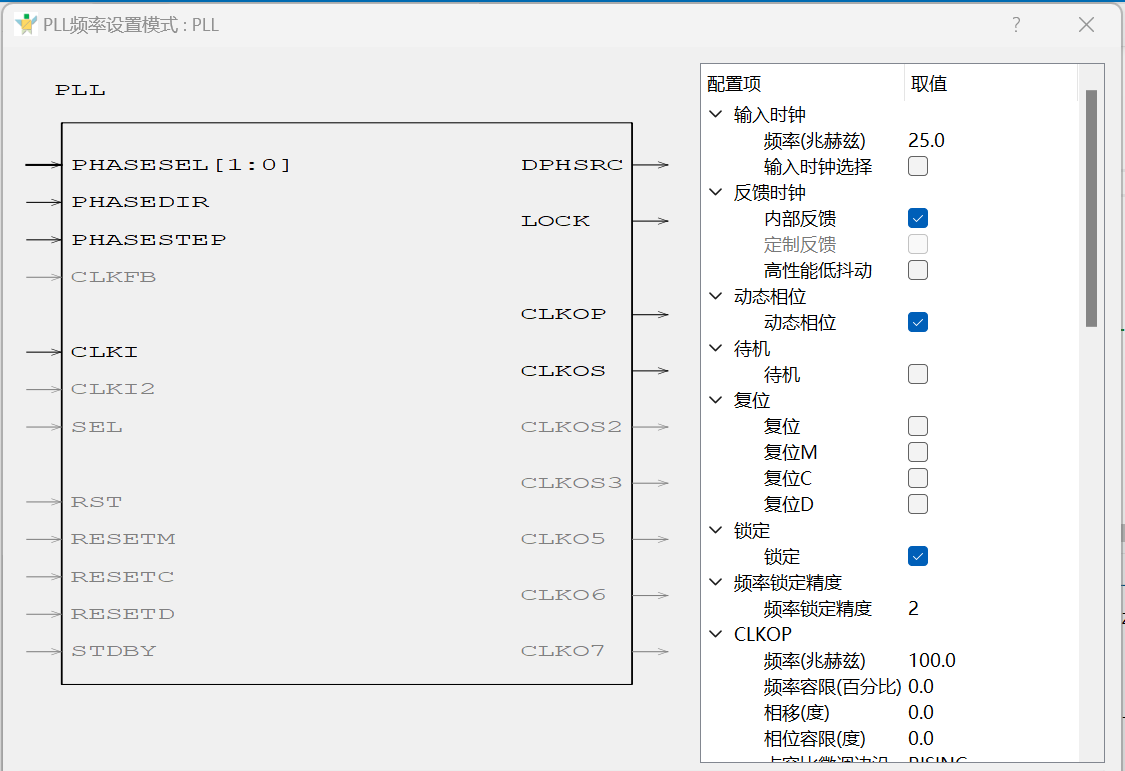

维多利亚老品牌vic3308的PLL IP支持动态相位调解功效��。在IP Creator中例化PLL的IP时���,翻开动态相位调解功效���,即可开启PLL输出时钟的相位动态调解��。

IP例化示例图

在勾选了动态相位之后���,IP会开启动态相位调解对应的信号接口��。其中PHASESEL[1:0]可选择做动态相位调解的输出端口���,“00”选择CLKOP通道���,“01”选择CLKOS通道���,“10”选择CLKOS2通道���,“11”选择CLKOS3通道����;PHASEDIR选择相位调解偏向���,“1”体现相位做正向调解���,“0”体现相位做负向调解����;PHASESTEP为动态相位调解的触发信号���,每一个脉冲实现一次相位调解��。

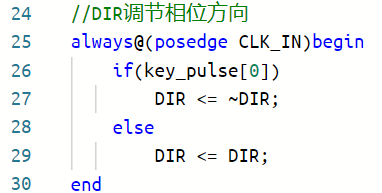

动态相位调解的实现代码如下所示���,通过按键切换动态相位调解的偏向

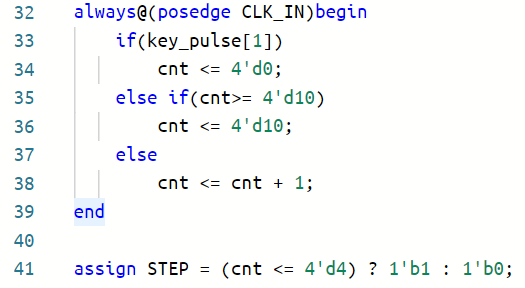

使用按键触爆发成动态调解的脉冲信号���,每一次按键���,完成一次相位调解

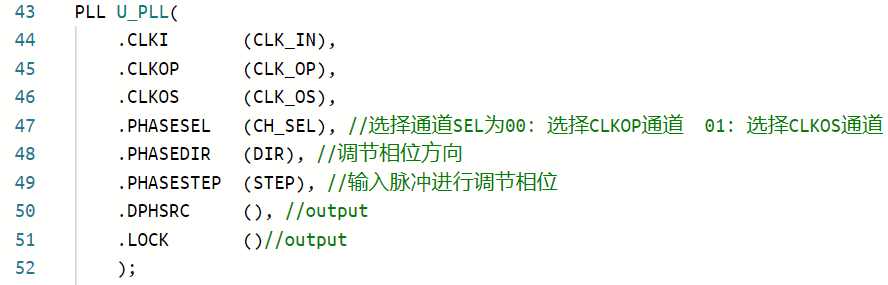

下图程序中���,CH_SEL为相位调解的时钟通道选择���,例程中设置为“01”���,即实现动态相位调解的通道为CLKOS

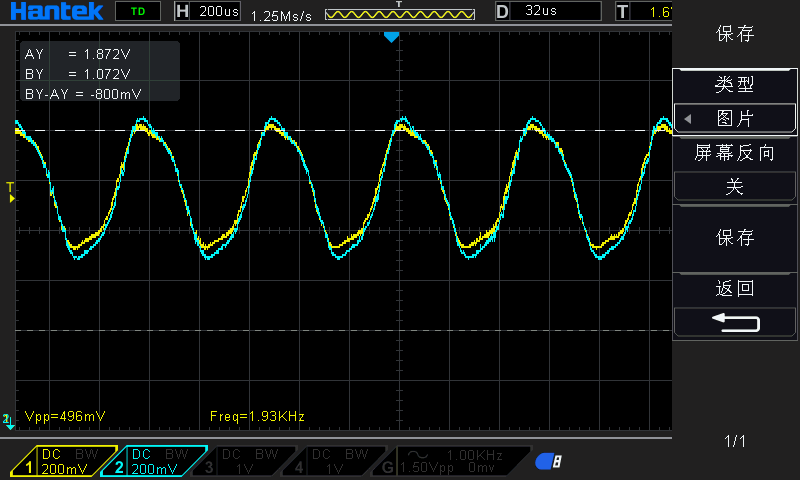

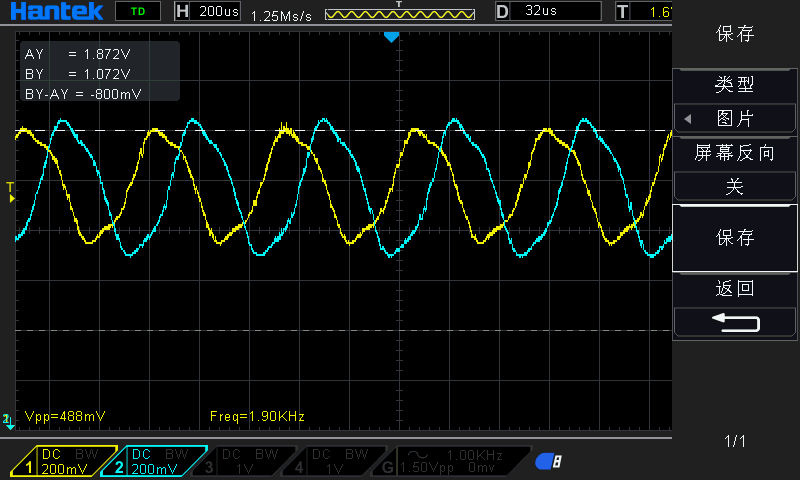

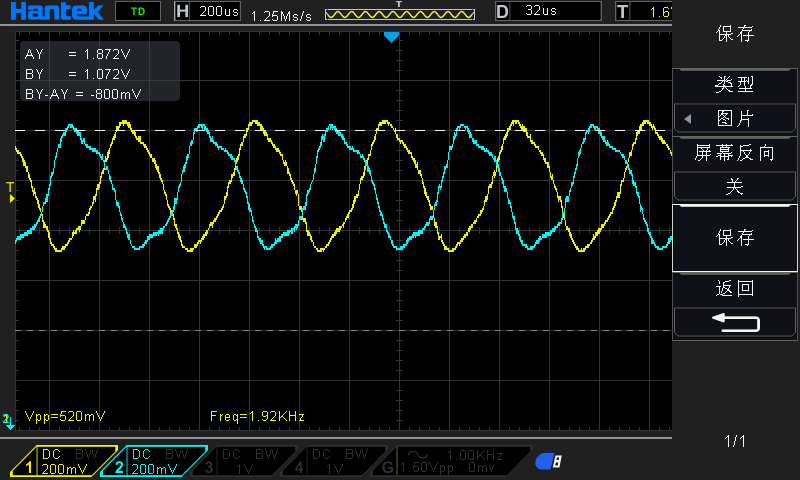

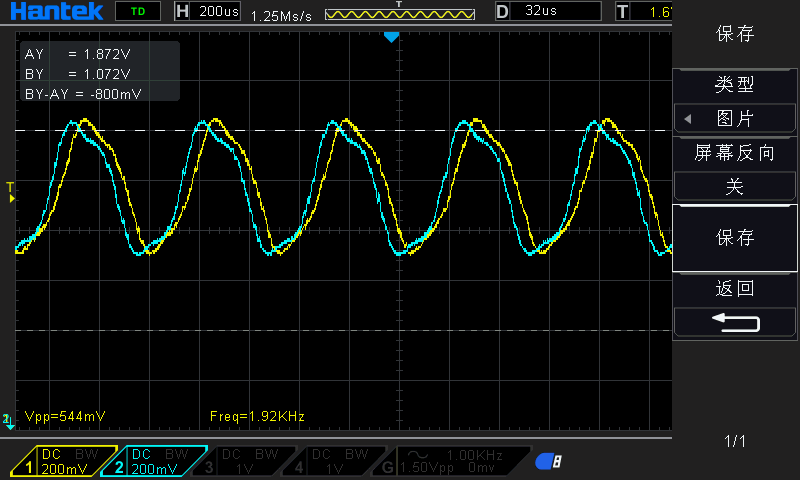

在测试中���,选择将CLKOP通道输出的时钟作为参考信号���,与CLKOS信号做比照��。划分选择了0次相位调解、18次相位调解、36次相位调解和54次相位调解���,其测试结果如下图所示��。实测60调解实现相位360°偏移��。

图1 初始相位

图2 18次相位调解

图3 36次相位调解

图4 54次相位调解

如有客户朋友需要获取源码���,请联系维多利亚老品牌vic3308的市场销售人员��。