1. 前言

本文将详细讲解如何使用ModelSim来仿真SA5T-100 SERDES��,这关于项目前期评估阶段的用户将有重要意义��,有助于快速熟悉和使用这颗100K逻辑的FPGA��。

2. 仿真情况

本文以ModelSim 10.1c情况为例来进行仿真历程的介绍��,也适用于其它版本��。

1)建库

由于目前SERDES仿真库是用两个vp文件提供的��,因此在建SEAL库的时候��,不要选xsSERDES_CH和xsSERDES_COM两个文件��,当用户仿真一个较大的工程时��,含有其它底层ip��,例如FIFO、双口RAM等��,就需要挪用这个SEAL库进行仿真了��。

2)SERDES库

目前以两个单独文件提供:

COMMON_WRAP.vp

SERDES_CH_windows.vp

3. 4通道SERDES代码架构

1)SA5T-100的SERDES程序结构是4个CHANNEL加1个COMMON��,参考时钟在SA5T-100是从COMMON输入的��,在4个CHANNEL均保存有GTGREFCLK的接口��。关于时钟部分��,一个Quad的SERDES包括4个CPLL和1个QPLL��,当速率低于6.6G��,使用CPLL即可��,高于6.6G则使用QPLL��,每条CHANNEL通道使用CPLL或是QPLL��,可以在代码中灵活配置��。

2)提供应用户的SERDES代码��,是以4通道的形式提供��,好比本仿真例程里的serdes_module_4CH.v��,这里面已经涵盖4个CHANNEL和1个COMMON��,并且把用户需要用到的参数都拉出来了��,易于修改使用��;引出来的通例接口��,以友商的SERDES?IP的接口命名方法给出��,用户易于理解和使用��。代码里也包括了SERDES的初始化复位流程��,包括复位CPLL/QPLL��,复位GTTXRESET和GTRXRESET��,同时也把用户控制GTTXRESET和GTRXRESET的使能引出来��,供用户随时进行复位控制��,具体可参阅serdes_module_4CH.v代码��。

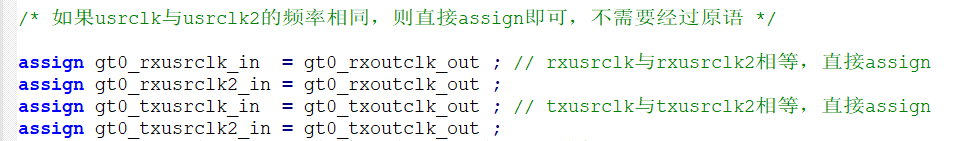

3)代码中usrclk时钟的使用

SERDES代码中每个CHANNEL通道有4个输入的usrclk时钟��,划分是:rxusrclk、rxusrclk2、txusrclk、txusrclk2��,它们都可以来自rxoutclk和txoutclk��,可是其频率关系是和SERDES内部位宽配置有关��,好比用户接口位宽是内部位宽的2倍��,那么rxusrclk2就即是rxusrclk的1/2��,本仿真例程里面��,用户接口位宽与内部位宽都是40bit��,因此可以直接把rxoutclk赋值给rxusrclk、rxusrclk2��,txoutclk赋值给txusrclk、txusrclk2��。

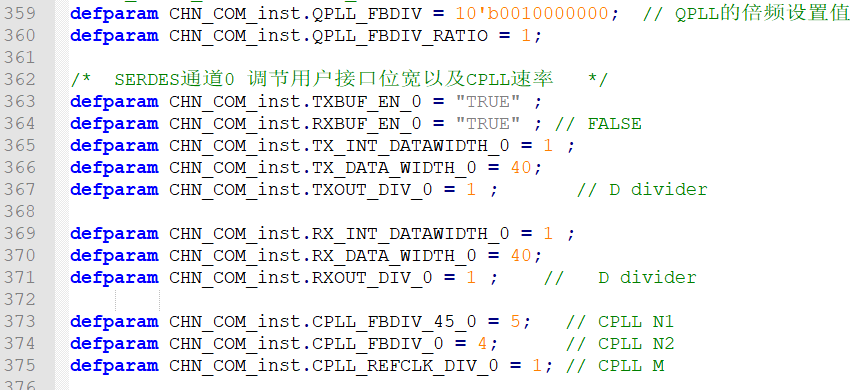

4)位宽、速率参数的配置

CPLL相关盘算公式:

fPLLClkout = fPLLClkin x (N1 x N2)/M ; ?

fLineRate ?= fPLLClkout x 2 / D

QPLL相关盘算公式:

fPLLClkout = fPLLClkin x N /(Mx2);

fLineRate ?= fPLLClkout x 2/ D

这些N1、N2、M、D参数的相关配置��,是通过代码中的defparam来通报��,具体可参考相应的代码:

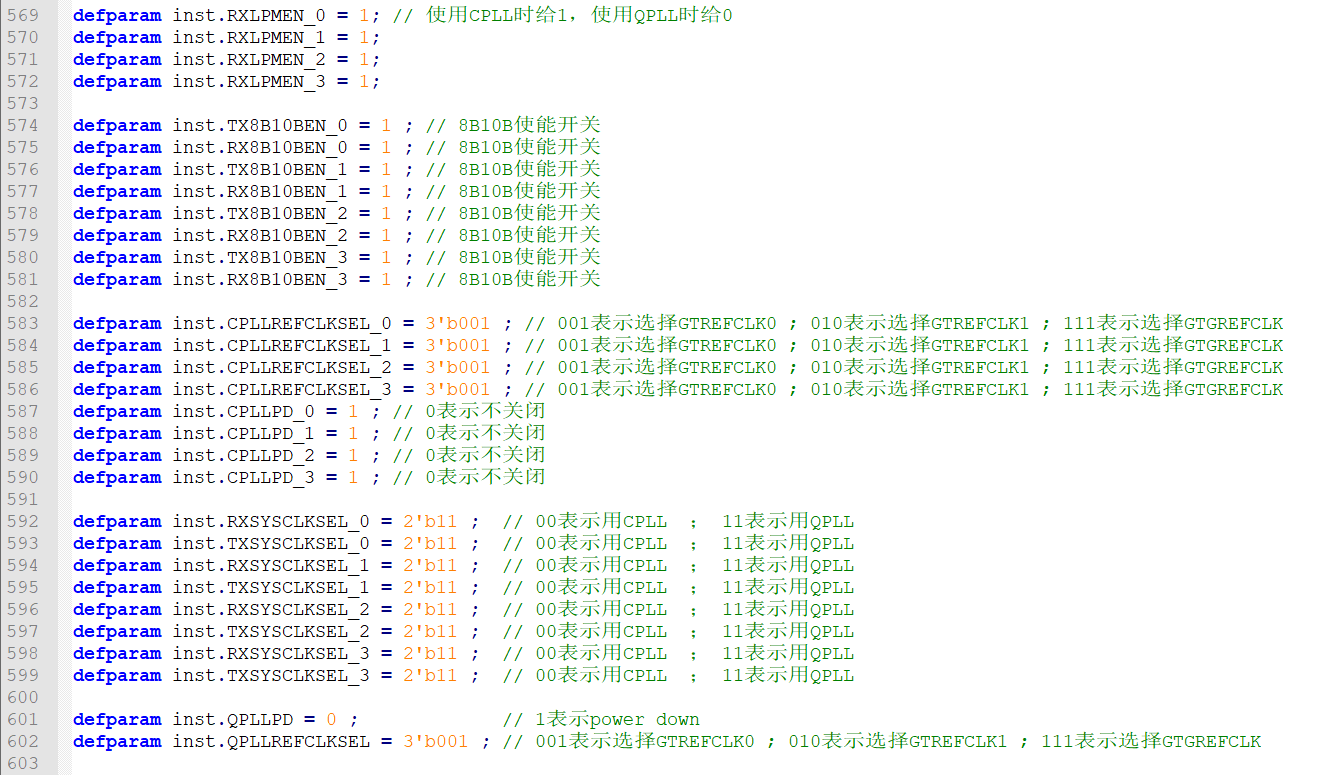

5)CPLL、QPLL选择项的配置

CPLL和QPLL的使用��,有几项配置需要注意��,目前在代码中都已经用parameter界说出来��,用户在挪用serdes_module_4CH.v时用defparam通报一下参数即可��,例如:

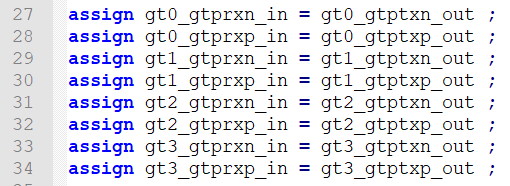

4. Testbench代码

1)在Testbench里��,需要结构出时钟给SERDES的参考时钟��,并写一段数据激励��,用于SERDES发送��,仿真时视察接收端数据情况��;可以配置loopback模式和PRBS模式��;也可以配置成正常模式��,并把txp/txn赋值给rxp/rxn��,组成一个外部环回的情况��,例如:

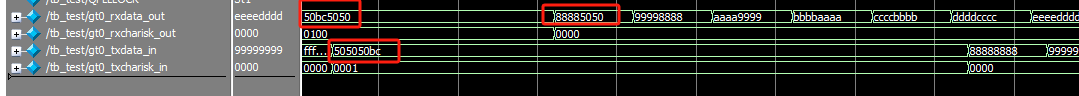

2)发送的激励数据��,是一段含K码的要害字+一段递增数据段��,K码为8’hBC��,在含有K码的字节中��,要相应把txcharisk拉高��,详细可参阅代码tb_test��。

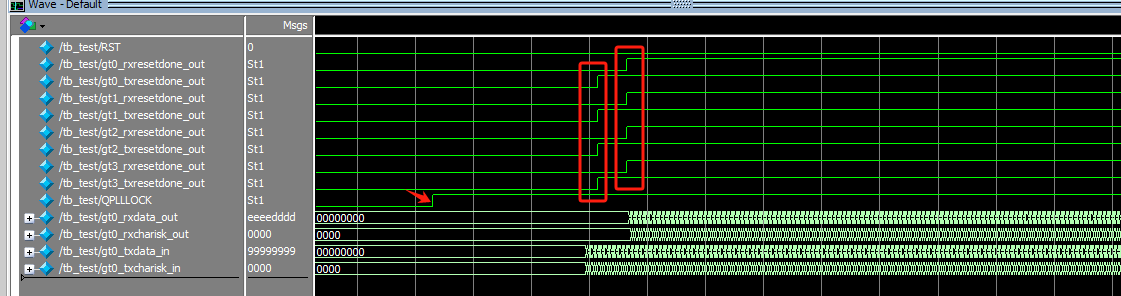

仿真时��,首先视察CPLL或QPLL有没有拉高��,再视察txresetdone和rxresetdone有没有拉高��,如果全部拉高则体现初始化结束��,再视察收发数据是否正常��。

仿真历程可以看出QPLL先锁定��,随后4个CHANNEL的rxresetdone和txresetdone也随即拉高��,体现SERDES复位乐成��,能进入接收状态��。

发送数据505050bc、88888888、99999999……

接收数据可以看到虽然有前后16bit的偏移��,可是K码的指示照旧准确的��,K码的作用就在这里��,用于指示并让用户能重新调理到正确的32bit数据��。

最后��,如果需要仿真例程的代码��,可以咨询销售或FAE��。